2010年9月の記事です。

≪2010年4月 2010年11月≫

書いた人: 新浜京都 | 10/09/04 00:23

はじめまして!Teamエレキ主任の浜です。実は、上級生不在のため、主任を務めるのはこれで2年目になります。「回路技術の向上」をモットーに、毎日活動を続けています。

実は、エレキは今、仮班所属の一年5人を除いて私一人で活動をしています。本来ですと、今までも「エレキ日記」として更新すべきでしたが、そこまで手が回らず、今回が初めてとなります。どうぞよろしくお願いします。

さて、ついに、回生ブレーキ回路が完成しましたので報告します。

エコノムーブでは、カーブを曲がるために減速する際、運動エネルギーを電気エネルギーに変換する、つまり、モーターを発電機として使用してキャパシタ―に充電し、そのときの逆電流によりブレーキをかける、いわゆる回生ブレーキを使用します。この際、バッテリ電圧を直接キャパシタに突っ込むと、エネルギーが半分失われてしまいます。そこで、PWM制御を使用すると、理論上ロスなく充電できることになります。また、任意のブレーキ力でブレーキをかけることができ、より高性能な制御をすることができます。これを制御するのがDC-DCコンバータであります。

今回のDC-DCコンバータはVer.3であり、高性能・高機能なものを製作しようと意気込み、気合いを入れて設計しました。今回の製品と特長は以下の通りです。

・タイミング良くフリーホイール用のFETをターンオンすることにより、順方向の降下電圧を減らし、効率を向上する同期整流技術を搭載した。

・入力電圧、出力電圧の変動にかかわらず、つまみ(可変抵抗)の角度に応じて入力電流の平均値電流を(±0.1Aの精度で)一定に制御できる。

・FETを4つ用いることにより、降圧と昇圧を連続で制御し、入力電圧と出力電圧の大小にかかわらず自由に電流を制御することが可能である。

(この写真は、降圧時非連続モードにおけるフリーホイール用FETの波形 同期整流ができていることに注目!!)

(こちらは昇圧時連続モード時の波形)

これらを設計、製作するにあたり、設計に緻密性・信頼性が要求されること、安全を担うシステムであることを今一度強く実感させられました。

主回路の回路図は以下の通りであります。

ご覧の通り、キャパシタの電位は下流側に入っているFETによって浮いています。このため、電子回路的にキャパシタ電流を測定することは(フォトカプラを使わずには)不可能となります。しかしながら、今回は回生ブレーキの回路であり、つまみの角度に対し、ブレーキ力が定まればよいわけですから、入力電流を監視すればよいということになります。このため、シャント抵抗はFETの下に入れればよいため、キャパシタの電位が浮いていても問題ないということになります(シャント抵抗は2mΩであるためFETのソース電位に影響を与えず波形が乱れる心配はない)。このように、ローサイドを制御する降圧回路と、同じくローサイドを制御する昇圧回路を組み合わせた形にしました。

//制御について

PWMのメインのプログラムは、DC-DCコンバータVer.1・Ver.2で使ったものを基本としました。このプログラムは、10kHzのPWMに同期させてPICのADコンバータで1周期120回測定することでフィードバック用の電流データを得ています。しかしながら、本当に10kHzの1周期、つまり100μs中に120回取ろうとしてもADコンバータの速度が遅く、ついていけません。それではどのような工夫をしているのかというと、1周期に2回データを取り、1周期ごとにタイミングをずらしていくようにして、結果として1周期に120回測定しているのと同じであるようにしています。確かにローパスフィルタを使って平滑化してやればこんなことをしなくて良いわけですが、ローパスフィルタの場合、方形波の場合を除いて、正しい平均値が得られるとは限りません。PWMの電流波形はインダクタンスの影響を受け、方形波にはなりません。このため、PWMに同期させてデータを取得し、より正確な平均値が得られるように努力しました。

結果としては、降圧から昇圧に入ると、値が0.1A程高くなって安定してしまいます。これはこの方法が完璧ではないことを意味している結果でもあります。これは、波形に、PWMによるノイズが含まれていることによると考えています。実際にはADコンバータ直前に1.8kΩと680μFを入れています。何も入れないともっと誤差が大きかったです。それでは、十分大きなコンデンサを入れて平滑化をしたらどうかというと、やはり、この方式よりは若干平均値電流の精度は落ちました。

これらの制御はアセンブリ言語で正確に時間を作りながら記述しています。

duty比の制御方式は、いわゆる「積分制御」に近い方式で制御しています。別に積分しているわけではなく、基準値とのずれの大きさを2通りに分類して、大きい場合は速く、小さい場合は遅く変化させるという方式をとっています。降圧側で全開になったら、昇圧側に入るという制御にしていますが、この中間に安定点が入ってしまうと制御が若干乱れることがあります。

//同期整流について

これは一歩間違えると大事故になりうる回路です。そのため、設計は慎重に行いました。

普通、同期整流というとmainのFETとコンプリメンタリな信号を、デッドタイムをつけてフリーホイール用のFETに送るというものですが、出力側がキャパシタであったり、モーターであったりして、逆向きの電圧が発生する場合には、これだと非連続モードのときに逆流してショートするおそれがあります。これを防ぐために、コンプリメンタリな信号とAND論理にして、電流の向きを検知して逆流する前にFETをオフにさせなければなりません。この検知をすることがミソということになります。電流を検知しようとシャント抵抗を入れるとロスになるし、FETの両端電圧を検出する方法にすると、検知した結果の動作によってまた電圧が変化するといったネガティブフィードバック的な動作になるということになります。また、これらの方法は電位的にばらばらなところに電子回路をおくことになり、やっかいなことになります。

そこで、肥後さんから教わった方法を使うことにしました。この方法は、とある企業の特許でありますが、非売品ということで認めさせてくださいということであります。

この方法は、コイルの電流が電圧の積分に比例するという特性を利用したものです。コイルに一周程度、導線を巻きつけ、この電圧を積分回路に通すことにより、三角波が得られ、再び電圧がゼロに近づいたとき、電流が逆流を始める直前だということになりますから、逆流を始める前にFETをカットオフにすることができるわけです。

この方法は最初に聞いたとき、感動しました。自分もこの方法には気付きませんでした。

この方法ですと、コイルに直接線をつないでいるわけではありませんから、電位を完全に分離することができ、設計が大幅に簡略化できるというわけです。

積分回路の結果をシュミットトリガー回路にかけるとタイミングの良い波形(方形波)が得られるのです。

//実用化するうえで、あらゆるシチュエーションを考える必要があった

実用化するうえでどんな状況(入力電圧・出力電圧・duty比・昇降圧・電源電圧の低下)にあっても、短絡や逆流は許されません。実験中の事故も極力避けたいので、設計は慎重を期しました。例えば、出力電圧が電源電圧を超えることは十分考えられ、この時に降圧モードに入り、逆流をすることは避けなくてはいけません。このため、電流値が一定値を下回るとこれを保護する動作に入ります。また、電源投入直後、シュミットトリガー回路がどちら側に入るかは偶然の要素で決まります。このことも考えなければなりません。また、電源電圧が降下してきた時、そのまま同期整流を続けさせていたのでは、同期整流のロジックが破綻し、直ちに短絡事故につながるおそれがあります。このため、電源が12Vを下回ると、ハイサイドドライバのIR2110がアンダーボルテージプロテクトになることを利用し、電子回路の電源が5Vを下回る前に同期整流を止めます。

ハイサイドの電源は、自作のチャージポンプで作り出しています。PICを使ってデッドタイムを作ることにより、信頼性を高めています。また、入力電圧が低くなると、チャージポンプから電源の一部が供給されるようにしています。FET駆動用の電源回路は工夫を凝らしています。

(FET駆動用の電源回路です。かなりコンパクトにしています。)

メインのFETをローサイドにもってきたのは、低電圧時でも駆動できるようにするため・ハイサイドにもっていくやり方より昇圧時に電流が通るFETの個数が少なくできるなどの理由からです。

//システム全体について

少々残念なのが、電子回路の消費電流が100mA近くあることです。オペアンプが結構食っているようです。電源にスイッチング式のものを使って消費電力を抑えたいです。

これからは、実際の車体に載せて性能を確かめていきたいです。

//実験時の事故について

実験時に一度事故を起こしました。コイルの巻き線が外れていたことによるもののようです。これが外れたため、同期整流のロジックが崩れ、キャパシタが短絡したまま保持されてしまったと考えられます。

ジジジ―と怪しげな音がしたので、これはまずいと思ったものの、キャパシタ回路を切断しなかったため、FET2つがものすごい勢いで白煙を上げ、小倉庫中に臭いが充満しました。大型扇風機をつけてもらい、周りの人たちには迷惑を掛けました。

対策としては、絶対にコイルの巻き線がずれないようにすることと、万一のためにキャパシタにブレーカーを入れることです。

それまでは一度も同様の事故を起こしたことはありませんでした。大電流の恐ろしさと、安全性を重視することの必要性を改めて思い知らされることになりました。

これが、爆発したFETです。良く見えませんが亀裂が入っています。

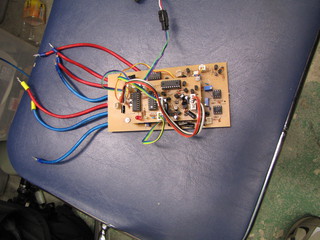

ここからは回路の写真です。

これは、main部とsub部を分けたところです。

コメントを全て読む / 書く

はじめまして!Teamエレキ主任の浜です。実は、上級生不在のため、主任を務めるのはこれで2年目になります。「回路技術の向上」をモットーに、毎日活動を続けています。

実は、エレキは今、仮班所属の一年5人を除いて私一人で活動をしています。本来ですと、今までも「エレキ日記」として更新すべきでしたが、そこまで手が回らず、今回が初めてとなります。どうぞよろしくお願いします。

さて、ついに、回生ブレーキ回路が完成しましたので報告します。

エコノムーブでは、カーブを曲がるために減速する際、運動エネルギーを電気エネルギーに変換する、つまり、モーターを発電機として使用してキャパシタ―に充電し、そのときの逆電流によりブレーキをかける、いわゆる回生ブレーキを使用します。この際、バッテリ電圧を直接キャパシタに突っ込むと、エネルギーが半分失われてしまいます。そこで、PWM制御を使用すると、理論上ロスなく充電できることになります。また、任意のブレーキ力でブレーキをかけることができ、より高性能な制御をすることができます。これを制御するのがDC-DCコンバータであります。

今回のDC-DCコンバータはVer.3であり、高性能・高機能なものを製作しようと意気込み、気合いを入れて設計しました。今回の製品と特長は以下の通りです。

・タイミング良くフリーホイール用のFETをターンオンすることにより、順方向の降下電圧を減らし、効率を向上する同期整流技術を搭載した。

・入力電圧、出力電圧の変動にかかわらず、つまみ(可変抵抗)の角度に応じて入力電流の平均値電流を(±0.1Aの精度で)一定に制御できる。

・FETを4つ用いることにより、降圧と昇圧を連続で制御し、入力電圧と出力電圧の大小にかかわらず自由に電流を制御することが可能である。

(この写真は、降圧時非連続モードにおけるフリーホイール用FETの波形 同期整流ができていることに注目!!)

(こちらは昇圧時連続モード時の波形)

これらを設計、製作するにあたり、設計に緻密性・信頼性が要求されること、安全を担うシステムであることを今一度強く実感させられました。

主回路の回路図は以下の通りであります。

ご覧の通り、キャパシタの電位は下流側に入っているFETによって浮いています。このため、電子回路的にキャパシタ電流を測定することは(フォトカプラを使わずには)不可能となります。しかしながら、今回は回生ブレーキの回路であり、つまみの角度に対し、ブレーキ力が定まればよいわけですから、入力電流を監視すればよいということになります。このため、シャント抵抗はFETの下に入れればよいため、キャパシタの電位が浮いていても問題ないということになります(シャント抵抗は2mΩであるためFETのソース電位に影響を与えず波形が乱れる心配はない)。このように、ローサイドを制御する降圧回路と、同じくローサイドを制御する昇圧回路を組み合わせた形にしました。

//制御について

PWMのメインのプログラムは、DC-DCコンバータVer.1・Ver.2で使ったものを基本としました。このプログラムは、10kHzのPWMに同期させてPICのADコンバータで1周期120回測定することでフィードバック用の電流データを得ています。しかしながら、本当に10kHzの1周期、つまり100μs中に120回取ろうとしてもADコンバータの速度が遅く、ついていけません。それではどのような工夫をしているのかというと、1周期に2回データを取り、1周期ごとにタイミングをずらしていくようにして、結果として1周期に120回測定しているのと同じであるようにしています。確かにローパスフィルタを使って平滑化してやればこんなことをしなくて良いわけですが、ローパスフィルタの場合、方形波の場合を除いて、正しい平均値が得られるとは限りません。PWMの電流波形はインダクタンスの影響を受け、方形波にはなりません。このため、PWMに同期させてデータを取得し、より正確な平均値が得られるように努力しました。

結果としては、降圧から昇圧に入ると、値が0.1A程高くなって安定してしまいます。これはこの方法が完璧ではないことを意味している結果でもあります。これは、波形に、PWMによるノイズが含まれていることによると考えています。実際にはADコンバータ直前に1.8kΩと680μFを入れています。何も入れないともっと誤差が大きかったです。それでは、十分大きなコンデンサを入れて平滑化をしたらどうかというと、やはり、この方式よりは若干平均値電流の精度は落ちました。

これらの制御はアセンブリ言語で正確に時間を作りながら記述しています。

duty比の制御方式は、いわゆる「積分制御」に近い方式で制御しています。別に積分しているわけではなく、基準値とのずれの大きさを2通りに分類して、大きい場合は速く、小さい場合は遅く変化させるという方式をとっています。降圧側で全開になったら、昇圧側に入るという制御にしていますが、この中間に安定点が入ってしまうと制御が若干乱れることがあります。

//同期整流について

これは一歩間違えると大事故になりうる回路です。そのため、設計は慎重に行いました。

普通、同期整流というとmainのFETとコンプリメンタリな信号を、デッドタイムをつけてフリーホイール用のFETに送るというものですが、出力側がキャパシタであったり、モーターであったりして、逆向きの電圧が発生する場合には、これだと非連続モードのときに逆流してショートするおそれがあります。これを防ぐために、コンプリメンタリな信号とAND論理にして、電流の向きを検知して逆流する前にFETをオフにさせなければなりません。この検知をすることがミソということになります。電流を検知しようとシャント抵抗を入れるとロスになるし、FETの両端電圧を検出する方法にすると、検知した結果の動作によってまた電圧が変化するといったネガティブフィードバック的な動作になるということになります。また、これらの方法は電位的にばらばらなところに電子回路をおくことになり、やっかいなことになります。

そこで、肥後さんから教わった方法を使うことにしました。この方法は、とある企業の特許でありますが、非売品ということで認めさせてくださいということであります。

この方法は最初に聞いたとき、感動しました。自分もこの方法には気付きませんでした。

この方法ですと、コイルに直接線をつないでいるわけではありませんから、電位を完全に分離することができ、設計が大幅に簡略化できるというわけです。

積分回路の結果をシュミットトリガー回路にかけるとタイミングの良い波形(方形波)が得られるのです。

//実用化するうえで、あらゆるシチュエーションを考える必要があった

実用化するうえでどんな状況(入力電圧・出力電圧・duty比・昇降圧・電源電圧の低下)にあっても、短絡や逆流は許されません。実験中の事故も極力避けたいので、設計は慎重を期しました。例えば、出力電圧が電源電圧を超えることは十分考えられ、この時に降圧モードに入り、逆流をすることは避けなくてはいけません。このため、電流値が一定値を下回るとこれを保護する動作に入ります。また、電源投入直後、シュミットトリガー回路がどちら側に入るかは偶然の要素で決まります。このことも考えなければなりません。また、電源電圧が降下してきた時、そのまま同期整流を続けさせていたのでは、同期整流のロジックが破綻し、直ちに短絡事故につながるおそれがあります。このため、電源が12Vを下回ると、ハイサイドドライバのIR2110がアンダーボルテージプロテクトになることを利用し、電子回路の電源が5Vを下回る前に同期整流を止めます。

ハイサイドの電源は、自作のチャージポンプで作り出しています。PICを使ってデッドタイムを作ることにより、信頼性を高めています。また、入力電圧が低くなると、チャージポンプから電源の一部が供給されるようにしています。FET駆動用の電源回路は工夫を凝らしています。

メインのFETをローサイドにもってきたのは、低電圧時でも駆動できるようにするため・ハイサイドにもっていくやり方より昇圧時に電流が通るFETの個数が少なくできるなどの理由からです。

//システム全体について

少々残念なのが、電子回路の消費電流が100mA近くあることです。オペアンプが結構食っているようです。電源にスイッチング式のものを使って消費電力を抑えたいです。

これからは、実際の車体に載せて性能を確かめていきたいです。

//実験時の事故について

実験時に一度事故を起こしました。コイルの巻き線が外れていたことによるもののようです。これが外れたため、同期整流のロジックが崩れ、キャパシタが短絡したまま保持されてしまったと考えられます。

ジジジ―と怪しげな音がしたので、これはまずいと思ったものの、キャパシタ回路を切断しなかったため、FET2つがものすごい勢いで白煙を上げ、小倉庫中に臭いが充満しました。大型扇風機をつけてもらい、周りの人たちには迷惑を掛けました。

対策としては、絶対にコイルの巻き線がずれないようにすることと、万一のためにキャパシタにブレーカーを入れることです。

それまでは一度も同様の事故を起こしたことはありませんでした。大電流の恐ろしさと、安全性を重視することの必要性を改めて思い知らされることになりました。

これが、爆発したFETです。良く見えませんが亀裂が入っています。

ここからは回路の写真です。

これは、main部とsub部を分けたところです。

外観です。